Introduction to Microprogram Sequencing

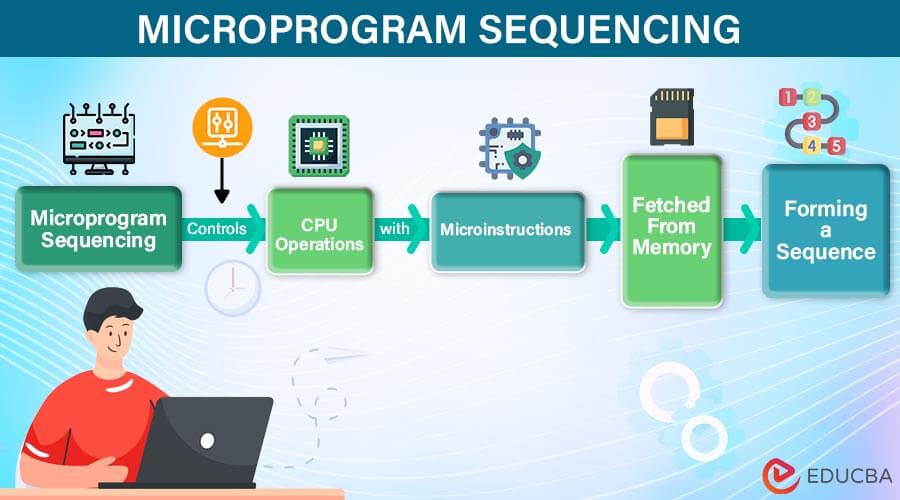

Microprogram sequencing, a complex yet vital component of CPU architecture, is pivotal for executing instructions precisely and efficiently. It serves as the linchpin in the operation of central processing units (CPUs), orchestrating the sequence of instructions from fetching to execution. Its significance lies in its role as the underlying mechanism governing modern computer systems’ inner workings. By managing instruction execution flow, microprogram sequencing ensures optimal performance and facilitates the implementation of complex instruction sets. A comprehensive understanding of this intricate process is essential for anyone delving into CPU architecture, as it forms the foundation for the functionality and effectiveness of CPUs.

Table of Contents

Importance of Microprogram Sequencing in CPU Architecture

- Instruction Execution Control: Microprogram sequencing governs the execution flow of instructions within the CPU. It coordinates the fetching, decoding, and execution phases of instruction processing, ensuring that each instruction is executed in the correct order and at the right time.

- Flexibility and Versatility: Unlike hardwired control units, microprogram sequencing offers high flexibility and versatility in controlling the CPU’s behavior. This flexibility enables easier implementation of complex instruction sets and facilitates future modifications or upgrades to the CPU architecture.

- Support for Complex Instruction Sets: Microprogram sequencing is particularly beneficial in CPUs supporting complex instruction sets, where instructions vary significantly in complexity and execution time. By providing a mechanism for precise control over instruction execution, microprogram sequencing allows for the efficient handling of diverse instruction types.

- Enhanced Performance: Efficient microprogram sequencing can improve CPU performance and optimize instruction execution. By minimizing the time spent on instruction fetching, decoding, and execution, microprogram sequencing contributes to overall system speed and responsiveness. This value holds immense importance in the world of CPU architecture.

- Fault Tolerance and Error Handling: Microprogram sequencing facilitates the implementation of error-handling mechanisms within the CPU architecture. It allows for the execution of error recovery routines and graceful handling of exceptional conditions, thereby enhancing the system’s fault tolerance and reliability.

- Simplified Instruction Set Architecture (ISA) Design: Microprogram sequencing enables the design of simplified instruction set architectures by offloading complex control logic from the hardware to the microcode. This abstraction simplifies the hardware design process and reduces the complexity of individual instruction implementations.

- Facilitation of Pipeline Execution: In pipelined CPU architectures, microprogram sequencing is essential for managing instructions flow through the pipeline stages. By coordinating the execution of instructions across multiple pipeline stages, microprogram sequencing helps maximize pipeline throughput and efficiency.

Basic Concepts

Microinstructions vs Instructions

Instructions

- Instructions are the fundamental commands or operations that a CPU can execute. They are part of the machine language understood by the CPU.

- Instructions are typically represented in binary format and correspond to specific actions such as arithmetic operations, data movement, or control flow changes.

- Instructions are directly executed by the CPU’s hardware, with each instruction triggering a series of microoperations that manipulate data and control signals within the CPU.

Microinstructions

- Microinstructions are low-level control signals used by the CPU’s control unit to execute instructions.

- Unlike instructions, which represent high-level operations visible to the programmer, microinstructions are internal to the CPU and are not directly accessible to programmers.

- Microinstructions control the CPU’s internal operations, including fetching instructions from memory, decoding them, executing arithmetic or logic operations, and updating the CPU’s state.

- Each instruction the CPU executes is broken down into a sequence of microinstructions, executed sequentially to perform the desired operation.

Control Unit and its Role in Microprogramming

The control unit is a crucial CPU component that coordinates and directs the processor’s operation. It interprets instructions fetched from memory and generates control signals to execute them.

Role in Microprogramming

- In microprogramming, the control unit plays a central role in executing instructions by generating and sequencing microinstructions.

- The control unit interprets the opcode (operation code) of each instruction fetched from memory and decodes it to determine the corresponding microinstructions required to execute the instruction.

- It generates control signals based on the decoded instruction, directing the CPU’s functional units (such as the arithmetic logic unit, registers, and memory) to perform the necessary microoperations.

- The control unit ensures that the microinstructions are executed in the correct sequence, coordinating the flow of data and control signals within the CPU.

- The control unit also manages fetching microinstructions from the microprogram memory and synchronizes their execution with the CPU’s clock signal.

Microinstruction Execution

- Upon fetching a new instruction from memory, the control unit decodes the instruction and determines the corresponding microinstruction sequence.

- It fetches these microinstructions instructions from the microprogram memory and generates the required control signals for their execution.

- The control unit coordinates the execution of microinstructions, ensuring that each microoperation is performed correctly and in the proper order to execute the instruction as intended.

Adaptability and Flexibility

- One of the advantages of using microprogramming is that it allows for the implementation of a flexible and adaptable control unit.

- The control unit can be easily modified or reprogrammed by changing the microinstructions stored in the microprogram memory, enabling updates to the CPU’s instruction set or behavior without altering the hardware design.

Microprogram Sequencer and its Functionalities

The microprogram sequencer, a control unit component, generates the address of the next microinstruction to execute during the instruction cycle. It controls the flow of microinstructions within the CPU and determines the sequence in which microinstructions execute to carry out the desired instruction.

Functionality of Microprogram Sequencer

- Address Generation: The microprogram sequencer’s primary function is to generate addresses corresponding to the next microinstruction to execute. It typically uses the current instruction’s opcode and other control signals to determine the following address.

- Control Flow Management: The microprogram sequencer manages the control flow within the microprogram by determining whether to proceed sequentially to the next microinstruction or branch to a different address based on conditional or unconditional branching conditions.

- Branching and Jumping: Besides sequential execution, the microprogram sequencer supports branching and jumping functionalities. It can execute conditional branches based on evaluating certain conditions, such as the status of flags or the result of a comparison operation. It can also execute unconditional jumps to specific addresses, allowing the implementation of subroutine calls or returns.

- Microprogram Counter (MPC) Management: The microprogram sequencer often includes a microprogram counter (MPC) in its design. The MPC keeps track of the address of the current microinstruction executing and updates it to point to the next microinstruction.

- Control Signal Generation: Alongside address generation, the microprogram sequencer generates control signals required for executing the current microinstruction. These control signals coordinate the operation of other components within the CPU, such as the arithmetic logic unit (ALU), registers, and memory.

Components of Microprogram Sequencer

- Control Logic: The control logic generates control signals that dictate the behavior of the microprogram sequencer. It interprets inputs such as the current microinstruction, external signals, and status flags to determine the appropriate actions, such as advancing to the next microinstruction or branching to a different address.

- Microinstruction Register (MIR): The microinstruction register (MIR) stores the microinstruction executed by the microprogram sequencer. It holds the opcode and other fields of the microinstruction, allowing the control logic to decode and interpret its contents.

- Microprogram Counter (MPC): The microprogram counter (MPC) keeps track of the following microinstruction address to be fetched and executed. It is typically implemented as a register or a set of flip-flops and is incremented or updated by the microprogram sequencer based on the control logic’s instructions.

- Address Generation Logic: The address generation logic computes the address of the next microinstruction based on the current microinstruction and any branching or jumping conditions specified. It may involve combinational logic circuits, multiplexers, and adders to calculate the following address accurately.

- Branching and Jumping Logic: The branching and jumping logic determines whether the microprogram sequencer should proceed sequentially to the next microinstruction or a different address based on conditional or unconditional branching conditions. It evaluates status flags, comparison results, or external inputs to make branching decisions.

- Control Signal Generation Unit: The control signal generation unit generates control signals required to execute the current microinstruction. These control signals activate or deactivate various functional units within the CPU, such as the arithmetic logic unit (ALU), registers, and memory, to perform the desired microoperations.

- Microprogram Memory Interface: The microprogram sequencer interacts with the microprogram memory, which stores the microinstructions. It includes interfaces for reading microinstructions from memory based on the address provided by the microprogram counter and writing control signals to the CPU’s control units.

Sequential Technique

Sequential Sequencing

Sequential sequencing is a straightforward approach to microprogram sequencing where microinstructions are executed sequentially, one after the other, without branching or jumping to different addresses. This sequential execution ensures that microinstructions are processed linearly, following the natural instruction execution flow within the CPU.

Advantages of Sequential Sequencing

- Simplicity: Sequential sequencing is simple to implement and understand, making it suitable for straightforward instruction sets and basic CPU architectures. The control logic for sequential sequencing is relatively uncomplicated, reducing design complexity.

- Determinism: Since the control unit executes microinstructions in a fixed sequence, the CPU’s behavior during instruction execution is deterministic and predictable. This predictability simplifies the debugging and testing process, as we can reliably anticipate the outcome of executing a sequence of instructions.

- Efficiency in Linear Instruction Streams: Sequential sequencing performs efficiently when executing instruction streams with minimal branching or conditional execution. Sequential sequencing minimizes the overhead of evaluating branching conditions and computing branch addresses in scenarios where most instructions execute without branching.

Limitations of Sequential Sequencing

- Inflexibility: Sequential sequencing lacks flexibility in handling complex control flow scenarios, such as loops, conditional execution, or subroutine calls. It cannot adapt dynamically to changing execution paths within the instruction stream, limiting its applicability in CPUs with complex instruction sets or non-linear execution patterns.

- Inefficient Handling of Branches: Sequential sequencing incurs overhead when encountering branches or jumps within the instruction stream. We must evaluate each branch instruction sequentially, even if the branch condition is known beforehand, leading to potential delays in instruction execution and reduced overall performance.

- Limited Support for Pipelining: Sequential sequencing may pose challenges in maximizing pipeline throughput in pipelined CPU architectures. The lack of support for speculative execution or branch prediction mechanisms can result in pipeline stalls and decreased efficiency, particularly in frequent branching instructions.

Branching Techniques

Conditional Branching

Definition

- Conditional branching involves evaluating a condition specified in the instruction or determined by the CPU’s state and deciding whether to branch to a different address based on the result.

- If the condition evaluates to true (i.e., the condition is satisfied), the microprogram sequencer branches to a target address corresponding to the true condition. Otherwise, it proceeds to the next instruction sequentially.

Implementation

- We implement conditional branching using dedicated branching instructions or conditional flags set by preceding instructions.

- The control logic evaluates the branching condition and determines the target address for branching based on the condition’s result.

- If the condition is true, the microprogram counter updates to the target address specified for that condition. If the condition is false, the microprogram counter updates to the target address specified for that condition.

Advantages

- Conditional branching enhances the flexibility and adaptability of microprogram sequencing by allowing the CPU to respond dynamically to changing conditions during instruction execution.

- It enables the implementation of conditional execution, loops, and decision-making constructs within the instruction set architecture, broadening the scope of applications supported by the CPU.

Subroutine Calls and Returns

Subroutine Calls

- Subroutine calls involve branching to a specific address where a subroutine is located and executing the sequence of microinstructions comprising the subroutine.

- Before branching to the subroutine address, the CPU typically saves the return address (the address of the next instruction after the subroutine call) to a designated register or memory location.

- Once the subroutine execution is complete, the CPU returns to the saved return address to resume the main program flow.

Subroutine Returns

- Subroutine returns involve transferring control back to the main program flow after completing the subroutine execution.

- Upon encountering a return instruction or reaching the end of the subroutine sequence, the CPU retrieves the saved return address and updates the microprogram counter to resume execution from that address.

Advantages

- Subroutine calls and returns promote code reuse and modular programming practices by enabling the encapsulation of commonly used sequences of microinstructions as subroutines.

- They simplify microprogram development and maintenance by reducing redundancy and improving code organization, leading to more manageable and maintainable microprograms.

Next Address Generation Logic

Microprogram Counter (MPC)

- The Microprogram Counter (MPC) is a register or a set of flip-flops used to store the next microinstruction address to be fetched and executed.

- The microprogram counter keeps track of the current position within the memory and updates the microprogram sequencer to point to the next microinstruction based on the control logic’s instructions.

Functionality

- The MPC is a pointer to the microprogram memory, indicating where to fetch the next microinstruction.

- During the instruction cycle, the microprogram sequencer updates the MPC based on the control logic’s instructions, either incrementing it to proceed to the next sequential microinstruction or modifying it to branch to a different address for conditional or unconditional branching.

Incrementing and Branching

- In sequential sequencing, the MPC typically increments after executing each microinstruction to proceed to the next microinstruction in the sequence.

- In branching scenarios, the MPC might update to a different address based on the branching conditions evaluated by the control logic. It allows the microprogram sequencer to redirect the control flow to a different part of the microprogram memory based on the current execution context.

Address Fields in Microinstructions

- Microinstructions often contain one or more address fields specifying the address of the next microinstruction to execute.

- These address fields may be encoded directly within the microinstruction or derived from additional control signals or status flags evaluated by the control logic.

Types of Address Fields

- Direct Addressing: The address field contains the direct memory address of the next microinstruction to fetch and utilize for sequential sequencing.

- Indirect Addressing: The address field contains a pointer or an offset that is added to the current value of the MPC to compute the address of the next microinstruction. We often use indirect addressing in branching scenarios, enabling more flexible control flow management.

- Conditional Addressing: The address field is selected based on the outcome of conditional branching conditions evaluated by the control logic. Different address fields may be specified for true and false conditions, enabling dynamic control flow decisions within the microprogram.

Role in Control Flow

- Address fields in microinstructions are crucial in determining the next microinstruction to execute during the instruction cycle.

- They provide the microprogram sequencer with the necessary information to fetch the correct microinstruction from the microprogram memory, ensuring the proper sequencing of microoperations within the CPU.

Error Handling and recovery in microprograms

- Error Detection:

- Microprograms incorporate mechanisms for detecting errors at various instruction execution stages, including instruction decoding, data processing, and memory access.

- Error detection techniques may involve parity checking, checksum verification, redundant computation, or comparison with expected outcomes to identify discrepancies or anomalies indicative of errors.

- Error Reporting:

- Upon detecting an error, the microprogram generates error signals or status flags to indicate the nature and location of the error.

- Error reporting mechanisms may involve setting error flags, generating interrupt signals, or triggering error handling routines to notify the system or the user of the error condition.

- Error Recovery:

- Error recovery mechanisms in microprograms aim to mitigate the effects of errors and restore the system to a stable and operational state.

- Recovery strategies may include retrying the erroneous operation, reverting to a known safe state, executing error correction routines, or initiating system shutdown or recovery procedures.

- Depending on the severity and type of error, the microprogram may automate recovery actions or require intervention from external software or hardware components.

- Redundancy and Error Correction:

- Microprograms may incorporate redundancy and error correction techniques to enhance fault tolerance and error resilience.

- Redundancy techniques such as dual-modular redundancy (DMR) or triple-modular redundancy (TMR) duplicate critical components or operations within the microprogram to detect and correct errors through voting or comparison mechanisms.

- Error Recovery Routines:

- Microprograms may include predefined error recovery routines or exception-handling mechanisms to address specific error scenarios.

- These routines may involve error logging, diagnostic procedures, data recovery, system reinitialization, or graceful degradation to ensure continued operation in the presence of errors.

Conclusion

Microprogram sequencing is a cornerstone in CPU architecture, directing instruction execution meticulously and effectively. By employing techniques like sequential sequencing, branching, and error handling, microprograms empower CPUs to handle intricate tasks with steadfast reliability and adaptability. Core components such as the Microprogram Sequencer, Control Unit, and Address Generation Logic collaborate harmoniously to manage control flow and error resolution seamlessly. Microprograms bolster system resilience and mitigate faults by integrating error-handling mechanisms. Microprogram sequencing is a pivotal force in shaping the capabilities and efficiency of contemporary computing systems.

Frequently Asked Questions (FAQs)

Q1. Can microprogram sequencing be modified or updated after CPU fabrication?

Answer: Microprogram sequencing can be modified or updated post-fabrication by reprogramming the microprogram memory. This flexibility allows for implementing new instructions, bug fixes, or optimizations without requiring CPU hardware changes.

Q2. How does microprogram sequencing support pipelined CPU architectures?

Answer: In pipelined CPU architectures, microprogram sequencing coordinates instructions flow through pipeline stages by ensuring each stage receives the appropriate microinstruction at the correct time. This coordination maximizes pipeline throughput and efficiency.

Q3. What role does microprogram sequencing play in enhancing CPU scalability?

Answer: Microprogram sequencing facilitates CPU scalability by providing a modular and flexible approach to control unit design. As CPU architectures evolve and expand, microprogram sequencing allows for the seamless integration of new instructions or features without significant hardware modifications.